# EE 435

# Lecture 40

# **Data Converters**

• Noise

**Review from Last Lecture**

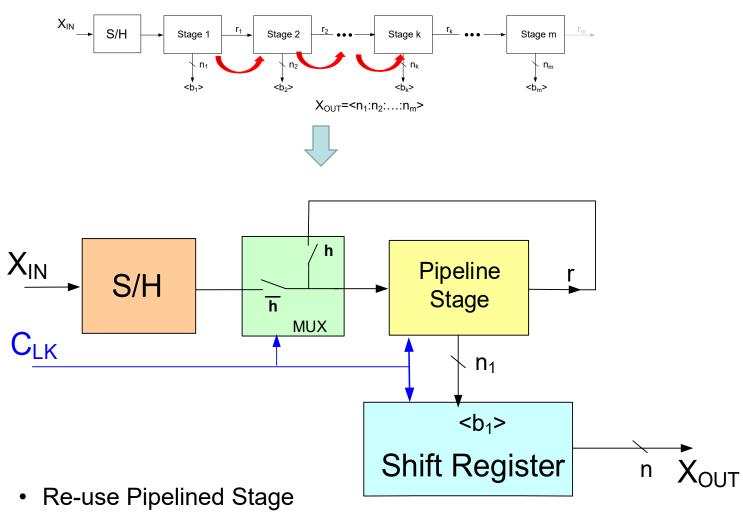

# Cyclic (Algorithmic) ADC

- Small amount of hardware

- Effective thru-put decreases

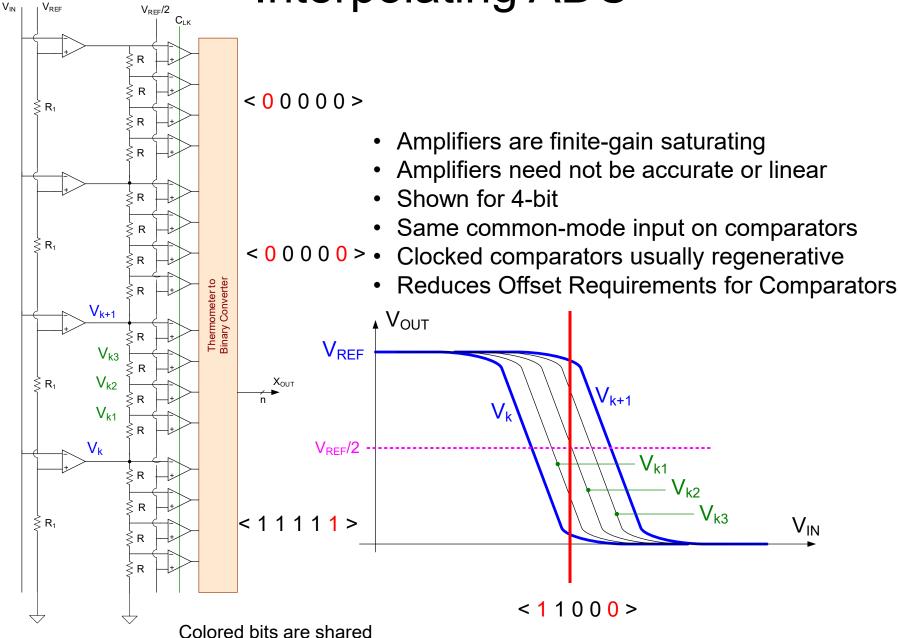

#### Review from Last Lecture Interpolating ADC

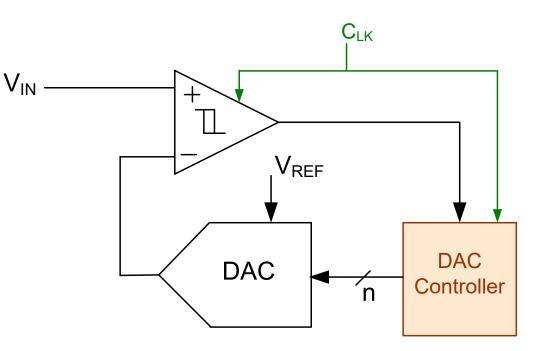

- DAC Controller may be simply U/D counter

- Binary search controlled by Finite State Machine is faster

- SAR ADC will have no missing codes if DAC is monotone

- Not very fast but can be small

- Any DAC can be used

- Single comparator !

**Review from Last Lecture**

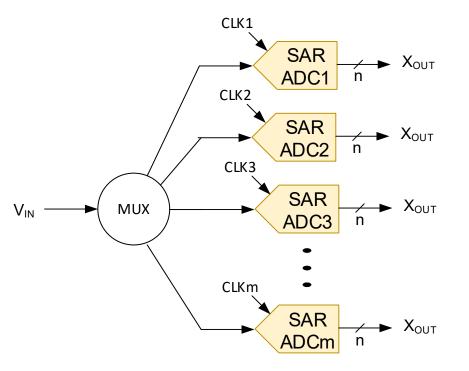

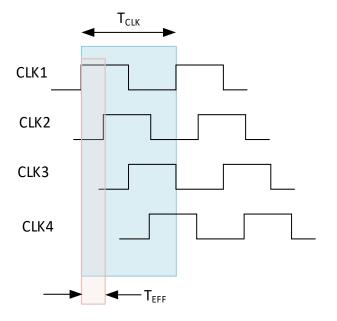

### **Time Interleaved SAR ADC**

Time interleaving increases effective conversion rate by factor of m

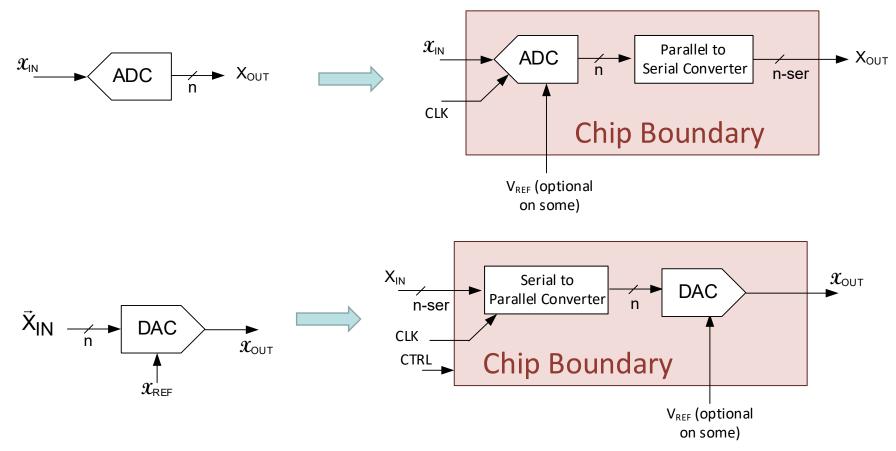

## Actual Catalog Data Converter Parts

- Often (not always) digital interface with data converter is serial

- Significantly Reduces pin count

- Interfaces usually follow standard protocols

- Challenge in data converter design almost always in the data converter itself

- Multiple channels often available and these usually use single converter and MUX

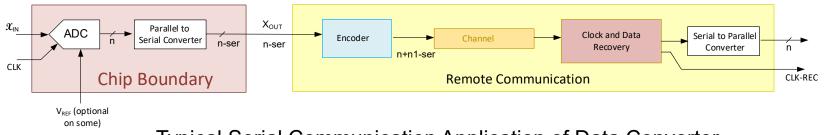

## **Common Application**

Want digital representation of analog input at a "distant" location

Distance could be a few cm or thousands of miles

Transmitting clock would dramatically increase communication overhead and provide no additional information

Keeping phase of clock aligned with data would be extremely difficult even for short distances

Data is usually encoded and at receiver end both clock and data are recovered (CDR)

Digital signals themselves degrade when passing through channel

Bit overhead is significant

Typical Serial Communication Application of Data Converter

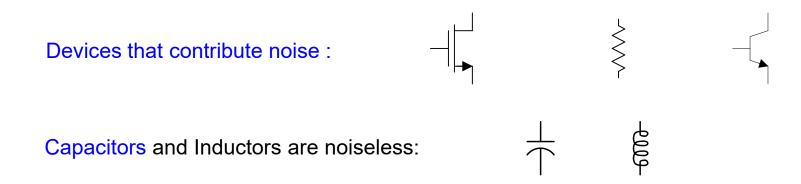

Noise in electronic devices and components introduce noise in electronic systems

Noise is of major concern in ADCs, DADs, and Op Amps

Beyond the scope of this course to go into lots of details about effects of device noise in these components but will provide a brief introduction

# Noise in DACs

Resistors and transistors contribute device noise but what about charge redistribution DACs ?

Noise in resistors:

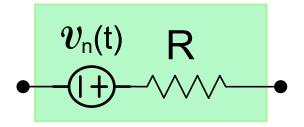

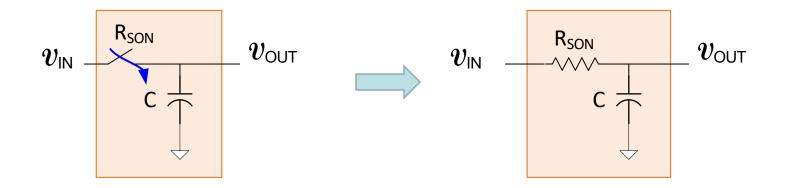

Noise can be characterized by either  $v_n(t)$  (time domain) or the spectral density S (frequency domain)

Noise spectral density of  $v_{\rm n}(t)$  at all frequencies for a resistor

- k: Boltzmann's Constant

- T: Temperature in Kelvin

k=1.38064852 × 10<sup>-23</sup> m<sup>2</sup> kg s<sup>-2</sup> K<sup>-1</sup> At 300K, kT=4.14 x10<sup>-21</sup>

$$S = 4kTR$$

## Noise in DACs

Resistors and transistors contribute device noise but what about charge redistribution DACs ?

Noise in linear circuits:

$v_n(t) \iff S(f)$

Typically interested in RMS value of the noise voltage

$v_{\scriptscriptstyle ext{RMS}}$

Time domain:

$$\boldsymbol{\mathcal{V}}_{\text{RMS}} = \sqrt{\lim_{T \to \infty} \frac{1}{T} \int_{t=0}^{T} \boldsymbol{\mathcal{V}}_{n}^{2}(t) dt}$$

Difficult to obtain directly !

Frequency domain:

$$ilde{\mathcal{V}}_{_{\!\!RMS}}=\sqrt{\int\limits_{\mathrm{f=0}}^{\infty}S(\mathrm{f})\,\mathrm{d}\mathrm{f}}$$

It can be shown that:

$$ilde{\mathcal{V}}_{_{\!\!RMS}}=\mathcal{V}_{_{\!\!RMS}}$$

## Noise in DACs

Resistors and transistors contribute device noise but what about charge redistribution DACs ?

Noise in linear circuits:

$$v_{n}(t)$$

$+$  T(s)  $v_{OUT}$

Due to any noise voltage source:

$$S_{_{\scriptscriptstyle VOUT}}=S_{_{\scriptscriptstyle V_n}}\left|T_{_n}(j\omega)

ight|^2$$

$$\mathcal{V}_{_{OUT_{RMS}}} = \sqrt{\int\limits_{\mathrm{f=0}}^{\infty}S_{_{VOUT}}\mathrm{df}}$$

Thus:

$$\mathcal{V}_{UUT_{RMS}} = \sqrt{\int_{f=0}^{\infty} S_{VUT} df} = \sqrt{\int_{f=0}^{\infty} S_{V_n} \left| T_n \left( j\omega \right) \right|^2 df}$$

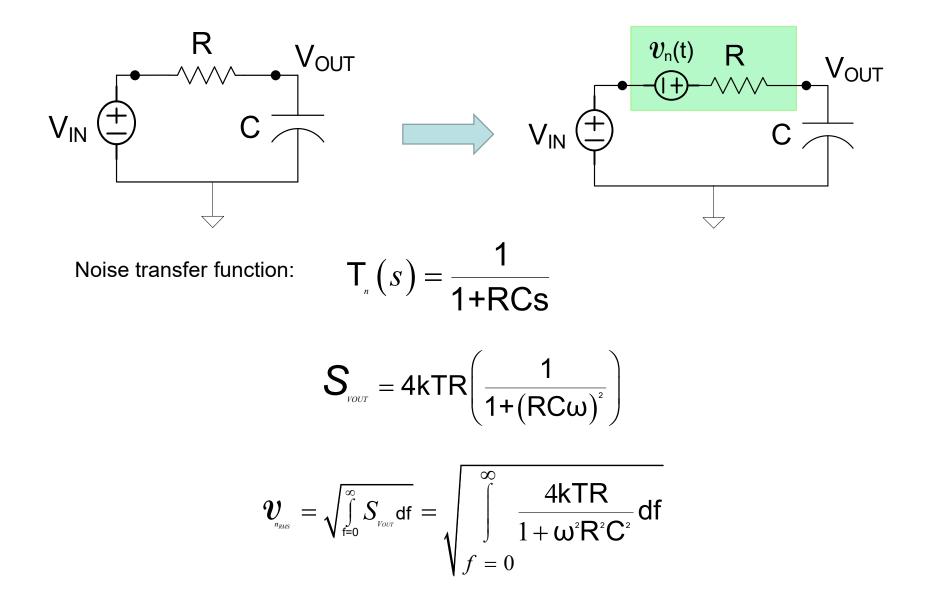

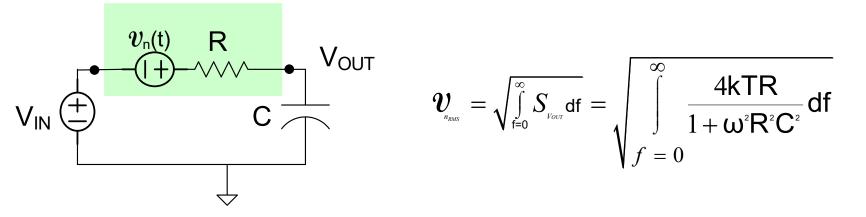

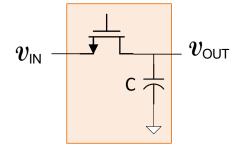

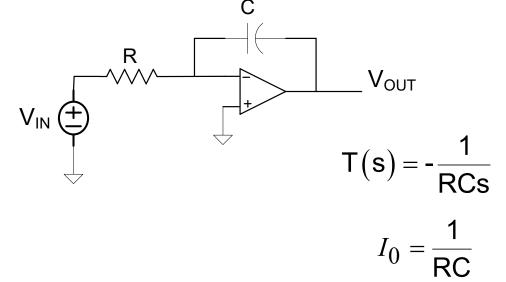

Example: First-Order RC Network

Example: First-Order RC Network

From a standard change of variable with a trig identity, it follows that

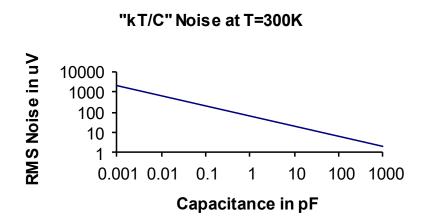

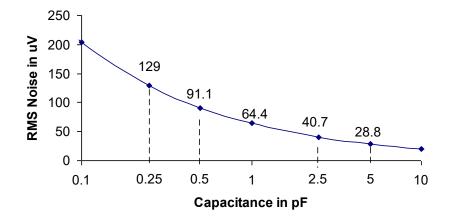

$$\mathcal{V}_{n_{RMS}} = \sqrt{\int_{f=0}^{\infty} S_{v_{OUT}} df} = \sqrt{\frac{kT}{C}}$$

- The continuous-time noise voltage has an RMS value that is independent of R

- Noise contributed by the resistor is dependent only upon the capacitor value C

- This is often referred to at kT/C noise and it can be decreased at a given T only by increasing C

"kT/C" Noise at T=300K

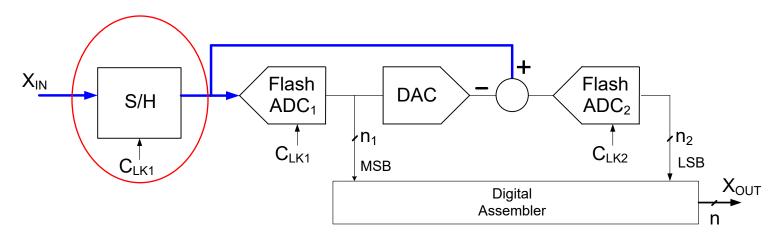

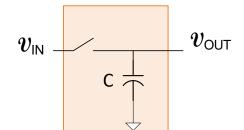

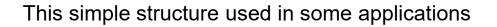

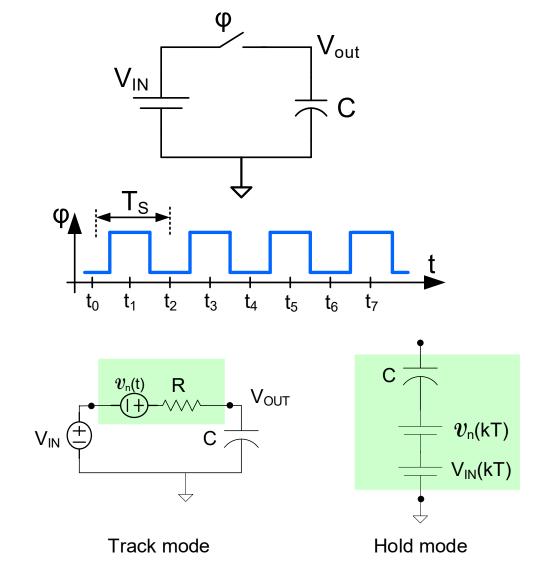

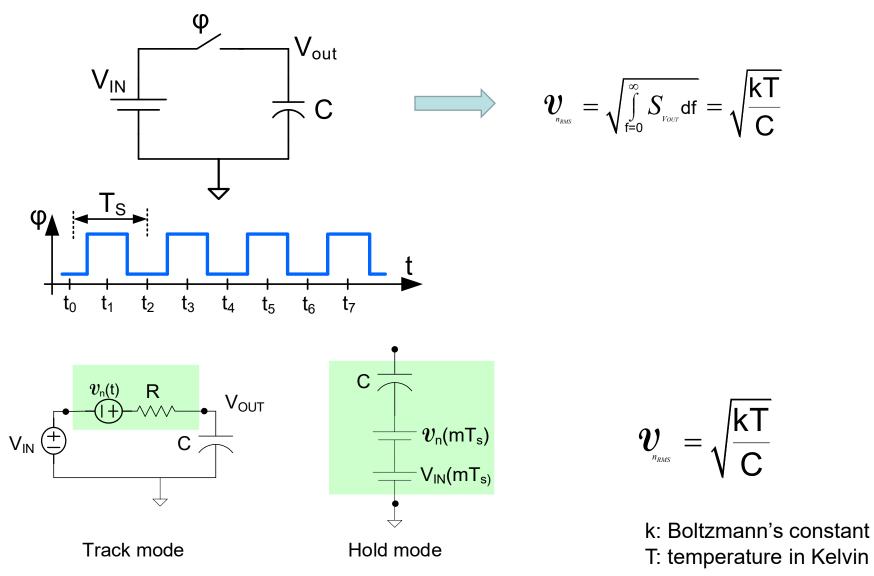

Actually a Track and Hold Circuit

Noise characteristics of S/H similar to that of these simple samplers

Basic S/H circuit

#### **During Track Mode**

When switch is opened to take sample, noise on C is captured on C (superimposed on signal)

This noise becomes input noise to the ADC

Recall noise in resistor modeled as noise voltage source in series with R

If switch opens fast, noise on C due to R is captured as  $v_{\rm n}({\rm kT})$

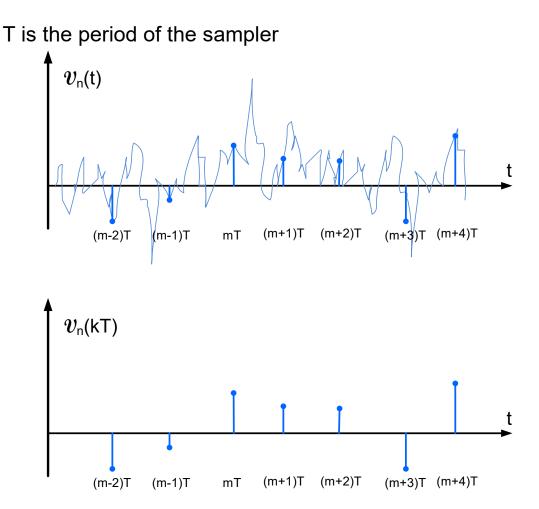

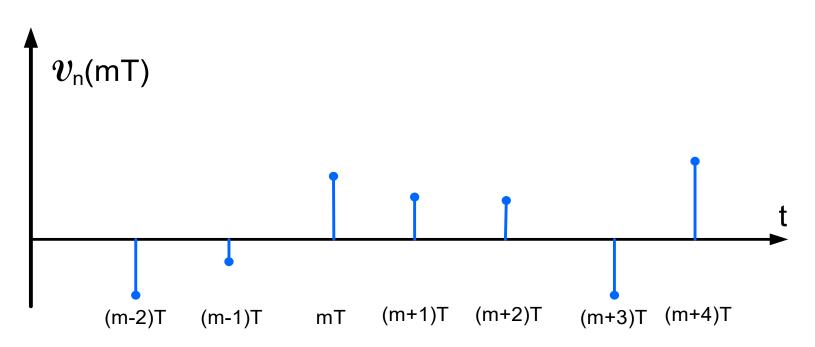

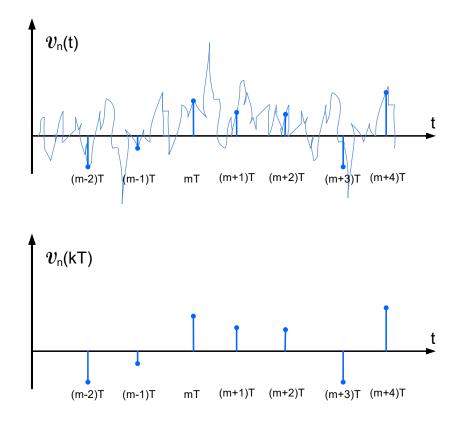

$\boldsymbol{\vartheta}_{n}(mT)$  is a discrete-time sequence obtained by sampling continuous-time noise waveform

RMS value of noise input to pipelined ADC is that of the discrete time noise sequence

Define the RMS noise of a discrete time noise sequence as

$$\boldsymbol{\hat{\mathcal{V}}}_{\text{\tiny RMS}} = E\left(\sqrt{\lim_{N \to \infty} \left(\frac{1}{N}\sum_{m=1}^{N} \boldsymbol{\mathcal{V}}^{2}\left(\text{mT}\right)\right)}\right)$$

Thus:

$$\boldsymbol{\hat{\mathcal{V}}}_{_{\mathrm{RMS}}} = E\left(\sqrt{\lim_{N \to \infty} \left(\frac{1}{N} \sum_{m=1}^{N} \boldsymbol{\mathcal{V}}^{2}\left(\mathrm{mT}\right)\right)}\right) \cong \sqrt{\frac{1}{N} \sum_{m=1}^{N} \boldsymbol{\mathcal{V}}^{2}\left(\mathrm{mT}\right)}$$

$v_n(mT)$  for each m is a random variable with some distribution function This distribution function is independent of m (i.e. the variables are identically distributed) Assume  $\mu_n$  is the mean and  $\sigma_n$  is the standard deviation of this random variable

#### What is the relationship, if any, between $v_{M}$ and $\hat{v}_{M}$

**Theorem 1** If v(t) is a continuous-time zero-mean noise source and  $\langle v(kT) \rangle$  is a sampled version of v(t) sampled at times T, 2T, .... then the RMS value of the continuous-time waveform is the same as that of the sampled version of the waveform. This can be expressed as  $v_{_{\rm RMS}} = \hat{v}_{_{\rm RMS}}$

**Theorem 2** If v(t) is a continuous-time zero-mean noise signal and  $\langle v(kT) \rangle$  is a sampled version of v(t) sampled at times T, 2T, .... then the standard deviation of the random variable v(kT), denoted as  $\sigma_v$  satisfies the expression  $\sigma = v = \hat{v}$

From Theorem 1 we obtain the RMS value of the switched capacitor sampler

RMS noise at output of basic SC S/H is independent of R but dependent upon C

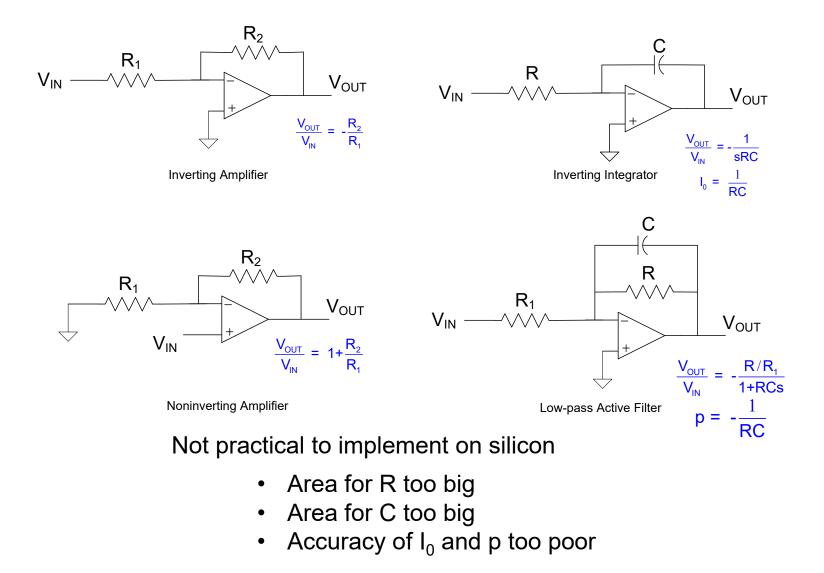

# Amplifiers and Filter on Silicon

- Finite Gain Amplifiers

- Filters

#### Some of the most basic and widely used analog circuits

But ratio accuracy can be very good (0.1% or better with good layout and appropriate area)

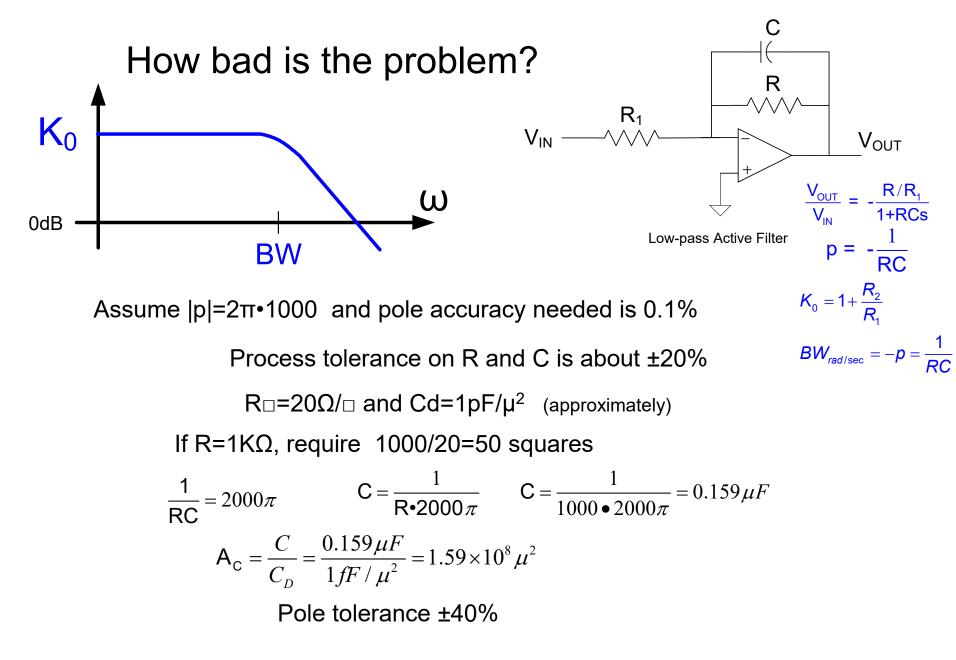

### How bad is the problem?

| PROCESS PARAMETERS   | N+ACTV P+ACTV POLY | PLY2 HR POLY | 2 MTL1  | MTL2 | UNITS   |

|----------------------|--------------------|--------------|---------|------|---------|

| Sheet Resistance     | 82.7 103.2 21.7    | 984 39.7     | 0.09    | 0.09 | ohms/sq |

| Contact Resistance   | 56.2 118.4 14.6    | 24.0         | )       | 0.78 | ohms    |

| Gate Oxide Thickness | 144                |              |         | ang  | strom   |

|                      |                    |              |         |      |         |

| PROCESS PARAMETERS   | MTL3 N\PLY         | N WELL       | UNITS   |      |         |

| Sheet Resistance     | 0.05 824           | 815          | ohms/sq |      |         |

| Contact Resistance   | 0.78               |              | ohms    |      |         |

|                      |                    |              |         |      |         |

COMMENTS: N\POLY is N-well under polysilicon.

| CAPACITANCE PARAMETERS      | N+ACTV | P+ACTV | POLY | POLY2 | M1 | M2 | M3 | N WELL | UNITS   |

|-----------------------------|--------|--------|------|-------|----|----|----|--------|---------|

| Area (substrate)            | 429    | 721    | 82   |       | 32 | 17 | 10 | 40     | aF/um^2 |

| Area ( <u>N+active</u> )    |        |        | 2401 |       | 36 | 16 | 12 |        | aF/um^2 |

| Area ( <u>P+active</u> )    |        |        | 2308 |       |    |    |    |        | aF/um^2 |

| Area (poly)                 |        |        |      | 864   | 61 | 17 | 9  |        | aF/um^2 |

| Area (poly2)                |        |        |      |       | 53 |    |    |        | aF/um^2 |

| Area (metall)               |        |        |      |       |    | 34 | 13 |        | aF/um^2 |

| Area (metal2)               |        |        |      |       |    |    | 32 |        | aF/um^2 |

| Fringe (substrate)          | 311    | 256    |      |       | 74 | 58 | 39 |        | aF/um   |

| Fringe (poly)               |        |        |      |       | 53 | 40 | 28 |        | aF/um   |

| Fringe (metall)             |        |        |      |       |    | 55 | 32 |        | aF/um   |

| Fringe (metal2)             |        |        |      |       |    |    | 48 |        | aF/um   |

| Overlap ( <u>N+active</u> ) |        |        | 206  |       |    |    |    |        | aF/um   |

| Overlap ( <u>P+active</u> ) |        |        | 278  |       |    |    |    |        | aF/um   |

$R_{\Box}=21.7\Omega/_{\Box}$  and  $Cd=0.864 fF/\mu^2$

#### Both are orders of magnitude unacceptable !

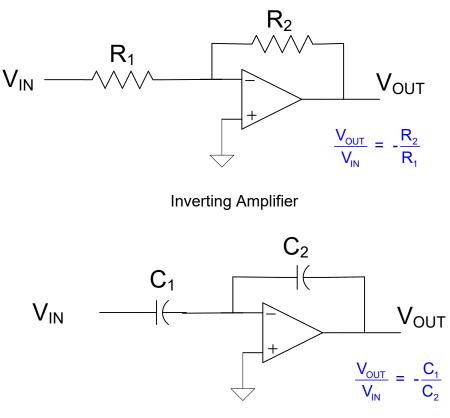

### An amplifier alternative ?

**Inverting Amplifier**

- Capacitor version is area effective and can have very good accuracy

- The node between C<sub>1</sub> and C<sub>2</sub> is a floating node if the Op Amp has a MOS differential pair at the input

- But if we get any charge on the intermediate node there is no way to get it off

### An amplifier alternative ?:

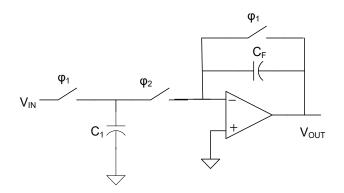

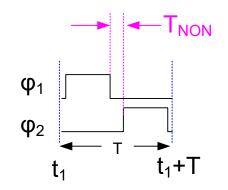

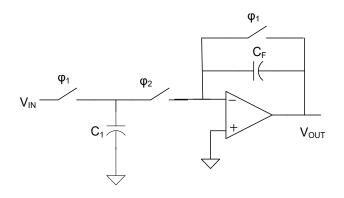

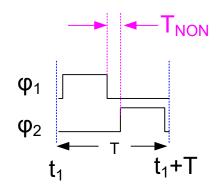

$\Phi_1$  and  $\Phi_2$  are nonoverlapping clocks

#### During $\Phi_1$

$C_1$  is charged to  $V_{IN}$  and stores charge  $Q_1 = C_1 V_{IN}$

$C_F$  is discharged and  $V_{OUT}=0$

During  $\Phi_2$

$C_{\rm 1}$  is discharged but charge is transferred to  $C_{\rm F}$

$Q_2$ =- $Q_1$  and  $V_{OUT}$ = $Q_2/C_F$

Substituting for  $Q_1$  we obtain  $V_{OUT} = -\frac{C_1}{C_2}V_{IN}$

Serves as a voltage amplifier with output valid during  $\varphi_2$

### An amplifier alternative !

$V_{OUT} = -\frac{C_1}{C_r}V_{IN}$

$\Phi_1$  and  $\Phi_2$  are nonoverlapping clocks

- Many applications only need amplifier output at discrete points in time

- Accuracy can be very good

- Area can be very small

But, what about the switches?

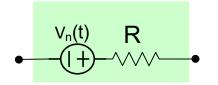

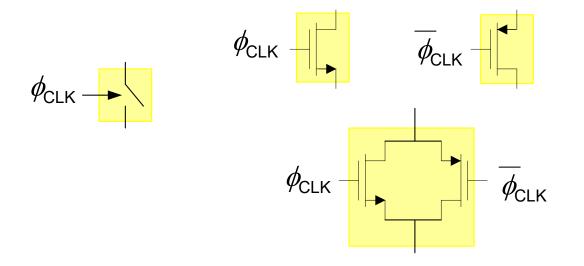

# Switches for SC Circuits

- Often a single MOS transistor is adequate (either n-ch or p-ch)

- Sometimes need transmission-gate switch (parallel n-ch and p-ch)

- Switches work very well and can be very small but must manage their R<sub>ON</sub>

And parasitic capacitors do not match very well

And parasitic capacitances may be highly nonlinear (junction capacitors)

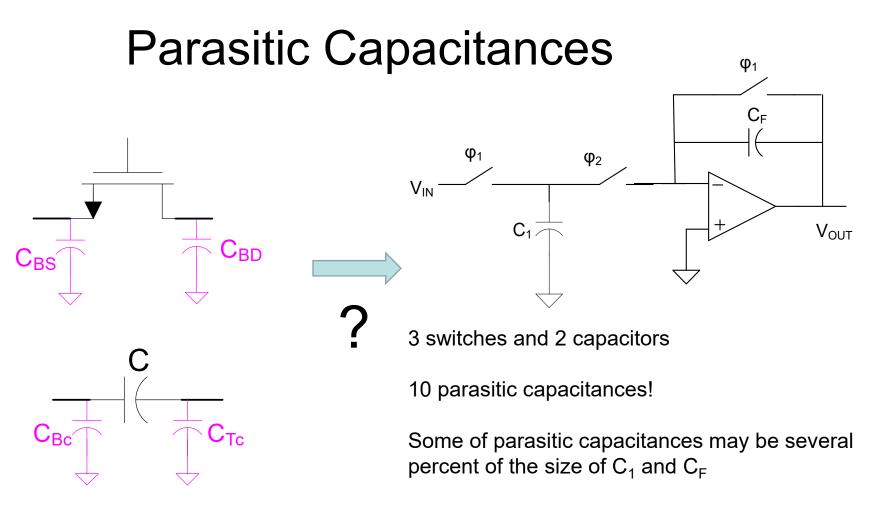

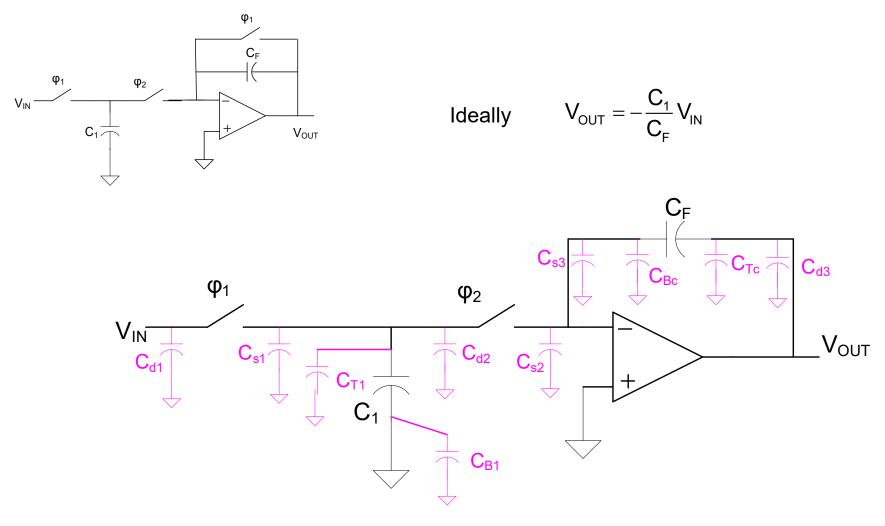

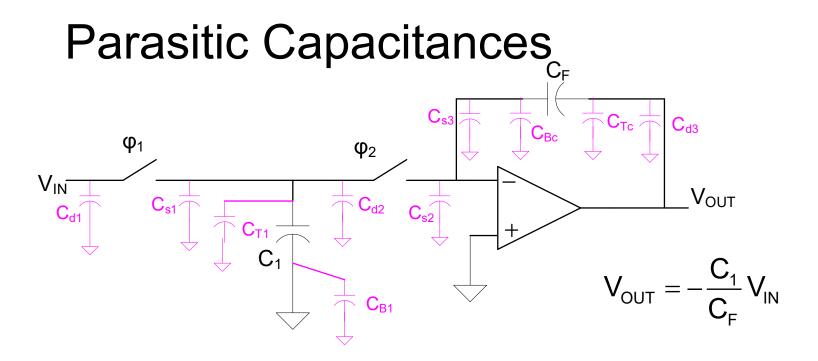

## **Parasitic Capacitances**

10 parasitic capacitances!

$C_1/C_F$  can be very precisely controlled with appropriate layout and area allocation

If op amp is ideal, C<sub>d1</sub>, C<sub>B1</sub>,C<sub>s2</sub>,C<sub>s3</sub>,C<sub>Bc</sub>,C<sub>Tc</sub> and C<sub>d3</sub> do not affect charge transfer !

But  $C_{s1}, C_{T1}, C_{d2}$  are all in parallel with  $C_1$  and all transfer charge

$$V_{OUT} = -\frac{C_1 + (C_{s1} + C_{T1} + C_{d2})}{C_r} V_{IN}$$

Parasitic capacitances not accurately controlled and dramatically degrade matching!

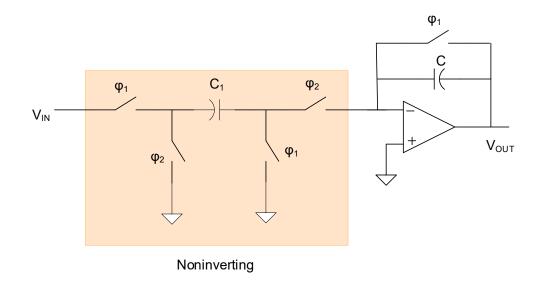

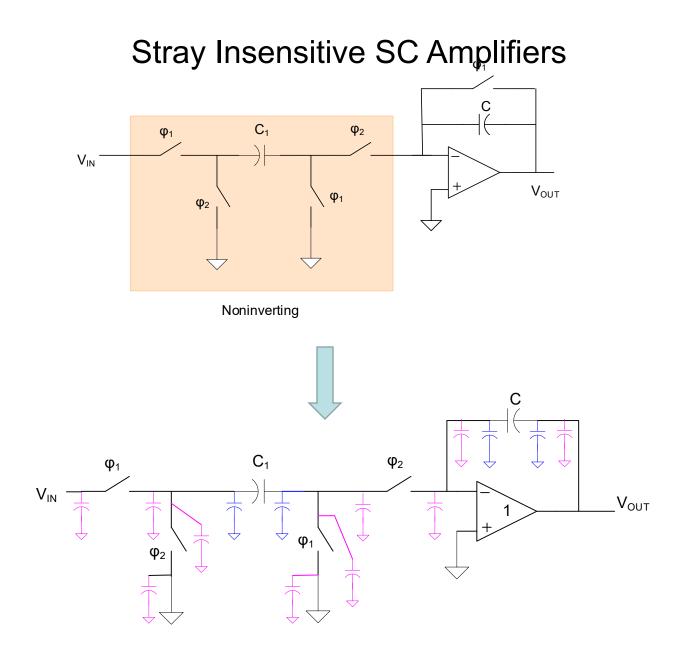

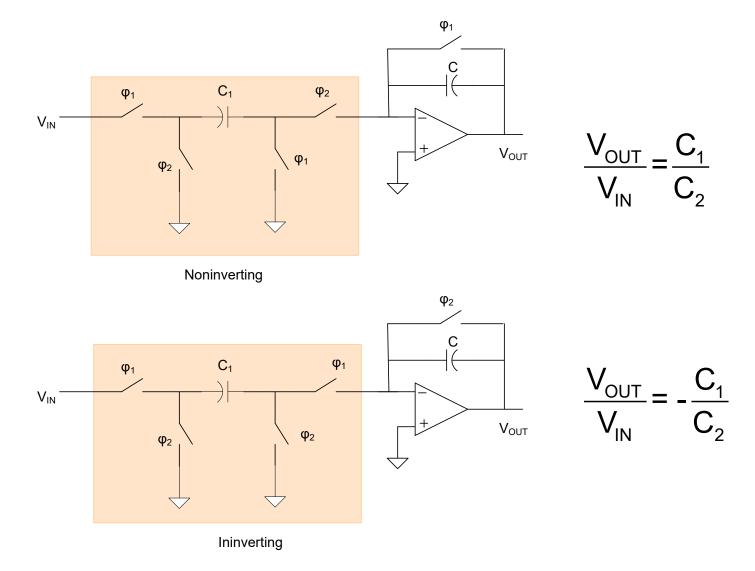

#### Stray Insensitive SC Amplifiers

Another SC Amplifier with even more switches !

Increased to 14 diffusion parasitic capacitances

Can show that all 14 diffusion parasitic capacitances do not affect gain !!

#### Stray Insensitive SC Amplifiers

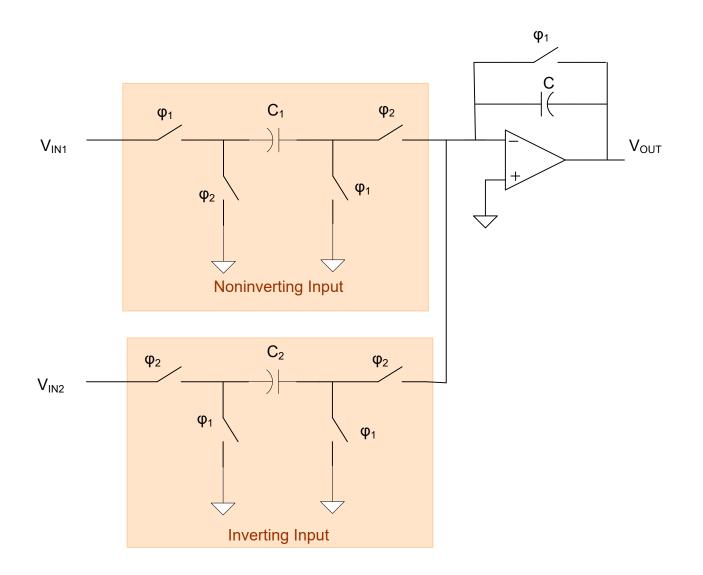

Can show that all diffusion parasitic capacitances do not affect gain Gain can be accurately controlled !

Summing amplifier inputs either inverting or noninverting can be easily obtained

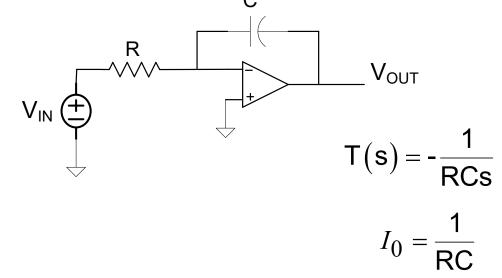

# Consider the $\mathop{\text{Basic}}_{\rm c}$ Integrator

Key performance of integrator (and integrator-based filters) is determined by the integrator time constant  ${\sf I}_0$

Precision of time constants of a filter invariably determined by precision of  $I_0$

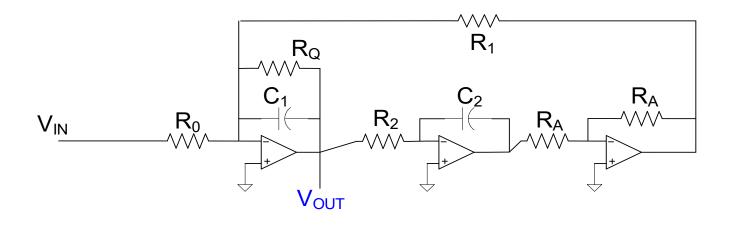

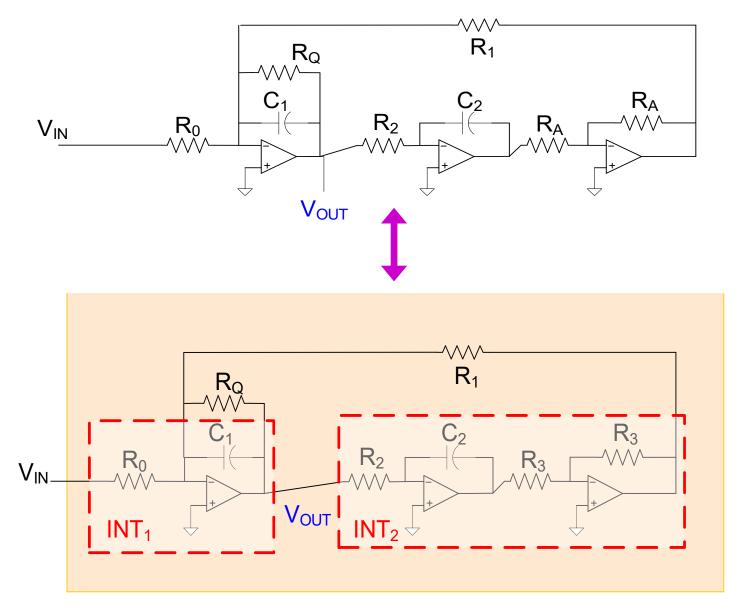

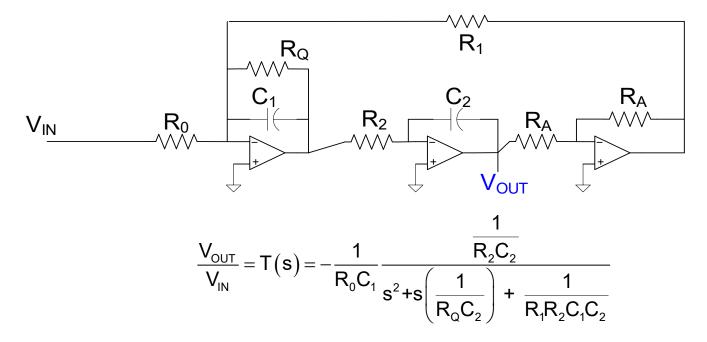

## **Integrator-Based Filters:**

$$\frac{V_{OUT}}{V_{IN}} = T(s) = -\frac{1}{R_0 C_1} \frac{s}{s^2 + s \left(\frac{1}{R_0 C_2}\right) + \frac{1}{R_1 R_2 C_1 C_2}}$$

Second-order Bandpass Filter

Denote as a two-integrator-loop structure

# **Integrator-Based Filters:**

## **Integrator-Based Filters:**

Second-order Lowpass Filter

Denote as a two-integrator-loop structure

- Any filter transfer function can be implemented with integrators and summers

- Some of the best known filter structures are based upon integrators and summers

- Accuracy of RC products is critical in the design of good filters

# **Consider the Basic Integrator**

Accurate control of I<sub>0</sub> is required to build good filters !

- 1. Accuracy of R and C difficult to accurately control particularly in integrated applications (often 2 or 3 orders of magnitude to variable)

- 2. Size of R and C unacceptably large if I<sub>0</sub> is in audio frequency range (2 or 3 orders of magnitude too large)

- 3. Amplifier GB limits performance

Appears to be Incredible Challenge to Building Filters on Silicon!

# Stay Safe and Stay Healthy !

# End of Lecture 40